# B.TECH DEGREE EXAMINATION,JANUARY 2023 THIRD SEMESTER INFORMATION TECHNOLOGY DIGITAL SYSTEM DESIGN PART-A(10X2=20 MARKS)

1.Write 16-bit 2'scomplement representation for the decimal number -28.

16-bit representation of decimal humber +28 is : (0000 0000 0001 1100) -28 is nothing but a's complement of +28. 1'S complement of +28: 1111 1111 1110 0011 2's complement of -28 is: 1111 1111 1110 0100

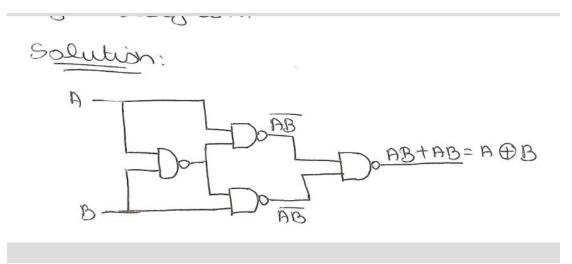

2.Find the minimum number of 2-input NAND gates required to implement a 2 input XOR gates and draw the logic diagram.

**3.A** four bit ripple carry adder is realized using 4 identical full adder. The carry propagation delay of each (FA) is 13ns. Calculate the worst case delay.

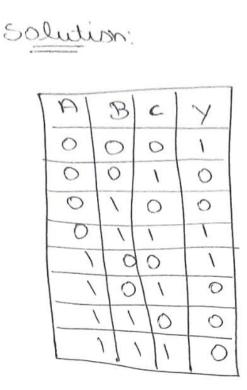

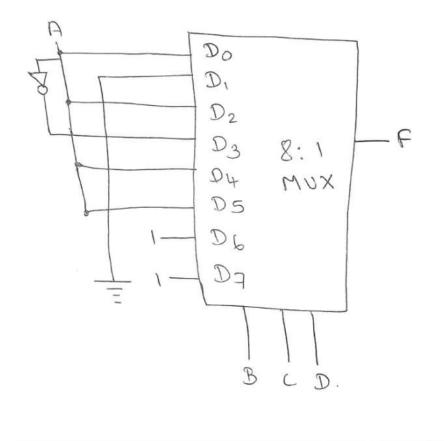

4.implement the given function using multiplexerF(A,B,C)= $\pounds_m(0,3,4)$ .

| Parameters             | Combinational Circuit                                                                                                                                        | Sequential CircuitIt is a type of circuit in which the output<br>does not only rely on the current input. It<br>also relies on the previous ones.                                                                                                                                                         |  |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Meaning and Definition | It is a type of circuit that<br>generates an output by relying<br>on the input it receives at that<br>instant, and it stays independent<br>of time.          |                                                                                                                                                                                                                                                                                                           |  |  |

| Feedback               | A Combinational Circuit<br>requires no feedback for<br>generating the next output. It is<br>because its output has no<br>dependency on the time<br>instance. | The output of a Sequential Circuit, on the<br>other hand, relies on both- the previous<br>feedback and the current input. So, the<br>output generated from the previous inputs<br>gets transferred in the form of feedback. The<br>circuit uses it (along with inputs) for<br>generating the next output. |  |  |

# 5.what is sequential circuit? How does it differ from combinational circuit?

# 6. Give the excitation table for D-FF AND T-FF.

# **D-FLIP FLOP**

| Q | Q⁺ | D |

|---|----|---|

| 0 | 0  | 0 |

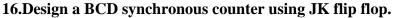

| 0 | 1  | 1 |

| 1 | 0  | 0 |

| 1 | 1  | 1 |

# **T-FLIP FLOP**

# Excitation table:

|   |    | - |

|---|----|---|

| Q | Q⁺ | т |

| 0 | 0  | 0 |

| 0 | 1  | 1 |

| 1 | 0  | 1 |

| 1 | 1  | 0 |

7.List the major difference between PAL AND PLA.

| S.NO | PLA                                              | PAL                                                                                   |

|------|--------------------------------------------------|---------------------------------------------------------------------------------------|

| 1.   | PLA stands for Programmable Logic<br>Array.      | While PAL stands for<br>Programmable Array Logic.                                     |

| 2.   | PLA speed is lower than PAL.                     | While PAL's speed is higher than PLA.                                                 |

| 3.   | The complexity of PLA is high.                   | While PAL's complexity is less.                                                       |

| 4.   | PLA has limited amount of functions implemented. | While PAL has a huge number of functions implemented.                                 |

| 5.   | The cost of PLA is also high.                    | While the cost of PAL is low.                                                         |

| 6.   | Programmable Logic Array is less<br>available.   | While Programmable Array<br>Logic is more available than<br>Programmable Logic Array. |

# 8. What are the steps for the design of asynchronous sequential circuit?

- 1. Create a state table or state diagram from the given problem statement.

- 2. Create a new reduced state table by removing all the redundant states.

- 3. Create the transition table.

- 4. Write the excitation and output Boolean equations and simplify them.

- 5. Draw the logic diagram.

# 9.Define gate-level modelling?

Gate level modeling is virtually the lowest level of abstraction because the switch-level abstraction is rarely used. Gate level modeling is **used to implement the lowest-level modules in a design, such as multiplexers, full-adder, etc.** Verilog has gate primitives for all basic gates.

## 10.Write the syntax for even construct.

A HDL is a domain specific language, specifically designed to support the description of digital logic circuits and clock driven sequential logic. As such a HDL contains **special constructs to enable the description of digital hardware and RTL elements**.

#### PART-B(5X11=55 MARKS)

#### UNIT 1

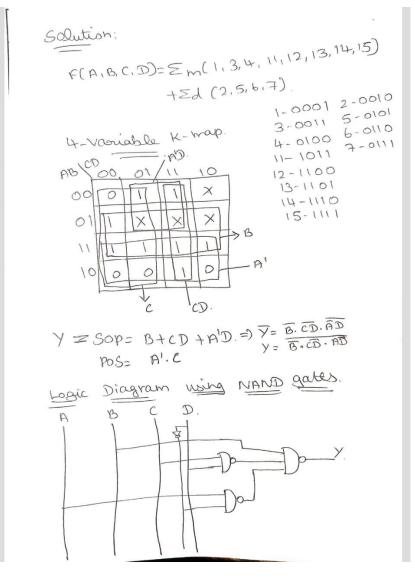

11.Simplify the following Boolean function using K-MAP and implement using only NAND gates  $F(A,B,C,D)=\pounds_M(1,3,4,11,12,13,14,15)+\pounds_D((2,5,6,7))$ .

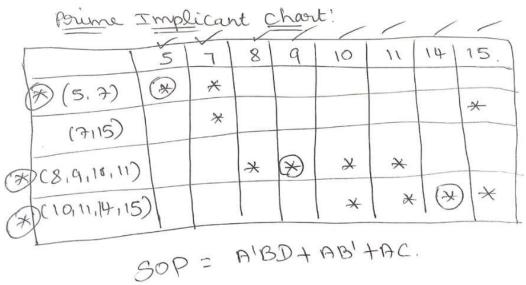

12. Minimize the given Boolean function using Quine McCluskey F(A,B,C,D) =M(5,7,8,9,10,11,14,15).

| Solution:<br>FLAIB, C.D.<br>Step1: Binoony e<br>Decimal<br>Number<br>5<br>7<br>8<br>9<br>10<br>11<br>14<br>15 | $) = \sum_{m} (5, 7)$<br>$p_{uivalent} fi p_{uivalent} fip_{uival}01010111100010011010101010101010101010101010101010101010101010101010101010101010101010101010101010101010101010101010101010101010101010101010101010101010101010101010101010101000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010001000100010000100010000100$ | D<br>1<br>0                                                                                            |

|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Stepz: <u>Gorouping</u> .<br>NO. of ones<br>1<br>2<br>3<br>4                                                  | Decimal<br>No.<br>8<br>9<br>10<br>7<br>11<br>14<br>15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Bincory<br>equivalent<br>1000-<br>1001-<br>1001-<br>1010-<br>0111-<br>1011-<br>1011-<br>1011-<br>1011- |

Step 3: 2- cell Gorouping.

$$2-cell$$

Binary equivalent.

(8:9) 100- -

(8:10) 100- -

(8:10) 10-0 -

(5:7) 01-1  $50$

(9:11) 101- -

(10:14) 101- -

(10:14) 1-10 -

(11:15) -111  $50$

(11:15) 1-11 -

(14:15) 1-11 -

Step 4: 4-cell Gorouping

| 4-cell          | Binary equivalent |

|-----------------|-------------------|

| (8,9,10,11)     | 10                |

| (8,10,9,11)     | 10 /              |

| (10, 11, 14,15) | 1 _ 1 _ /         |

| (10,14,11,15)   | 1 - 1 -           |

|                 |                   |

Step 5: Remove Replicant.

| 4-cell.           | Binasy equivalent |

|-------------------|-------------------|

| (8,9,10,11)       | 10                |

| (10, 11, 14, 15). | 1-1-              |

| ABCD<br>01-1 | n'b)  |

|--------------|-------|

| - 111        | BCD   |

| 10           | AB'   |

| 1-1-         | AC.   |

|              | - 111 |

| B | CD( | 842 | l) | Excess-3 |     |     |       |

|---|-----|-----|----|----------|-----|-----|-------|

| Α | В   | С   | D  | w        | x   | У   | z     |

| 0 | 0   | 0   | 0  | 0        | 0   | 1   | 1     |

| 0 | 0   | 0   | 1  | 0        | 1   | 0   | 0     |

| 0 | 0   | 1   | 0  | 0        | 1   | 0   | 1     |

| 0 | 0   | 1   | 1  | 0        | 1   | 1   | 0     |

| 0 | 1   | 0   | 0  | 0        | 1   | 1   | 1     |

| 0 | 1   | 0   | 1  | 1        | 0   | 0   | 0     |

| 0 | 1   | 1   | 0  | 1        | - 0 | - 0 | 1     |

| 0 | 1   | 1   | 1  | 1        | 0   | 1   | - 0 - |

| 1 | 0   | 0   | 0  | 1        | 0   | 1   | 1     |

| 1 | 0   | 0   | 1  | 1        | 1   | 0   | 0     |

| 1 | 0   | 1   | 0  | X        | X   | X   | X     |

| 1 | 0   | 1   | 1  | X        | X   | X   | X     |

| 1 | 1   | 0   | 0  | X        | Х   | Х   | Х     |

| 1 | 1   | 0   | 1  | X        | Х   | Х   | Х     |

| 1 | 1   | 1   | 0  | X        | Х   | Х   | Х     |

| 1 | 1   | 1   | 1  | X        | Х   | Х   | Х     |

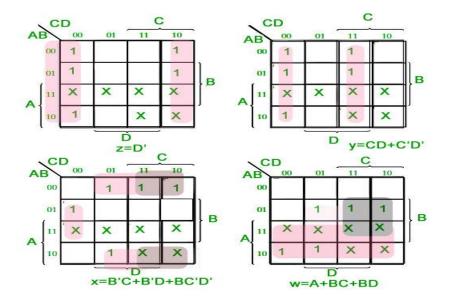

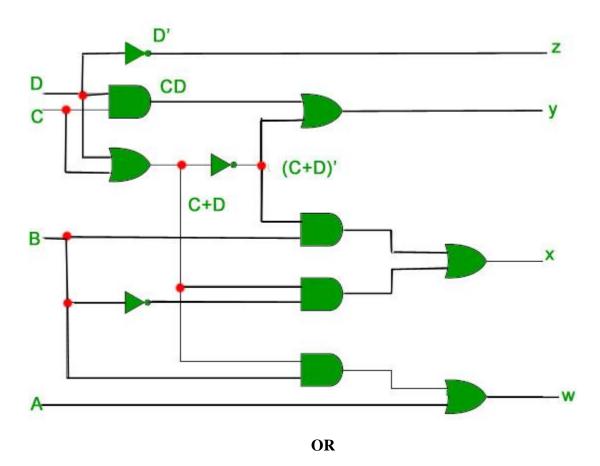

13.Design a circuit that converts BCD code to Excess-3 code converter.

To find the corresponding digital circuit, we will use the K-Map technique for each of the Excess-3 code bits as output with all of the bits of the BCD number as input.

Corresponding minimized Boolean expressions for Excess-3 code bits -

The corresponding digital circuit-

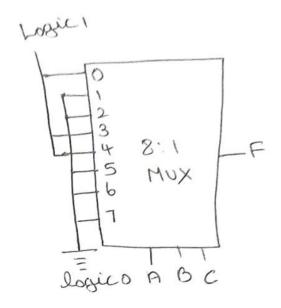

# 14.Implement the switching function $F=\pounds_M(3,6,7,8,10,12,13,14,15)$ using an 8 input multiplexer.

In the given boolean expression, there are 4 variables. We should use  $2^4 : 1 = 16 : 1$  multiplexer. But as per the question, it is to be implemented with 8 : 1 mux.

For 8 : 1 multiplexer, there should be 3 selection lines. So from the given 4 variables, the 3 least significant variables(B, C, D) are used as selection line inputs.

The 8 inputs are derived using the implementation table shown below

Forom the desired input 8:1 multiples, can be drawn as below.

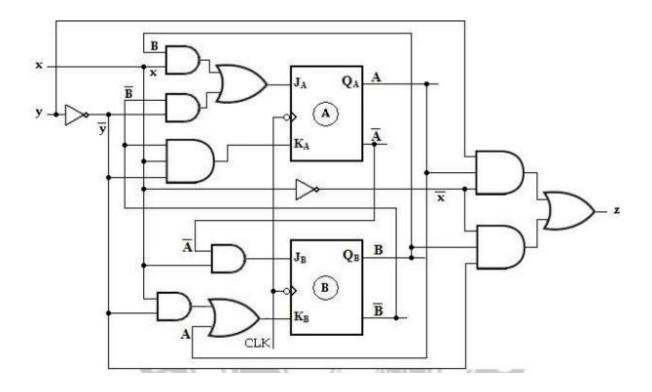

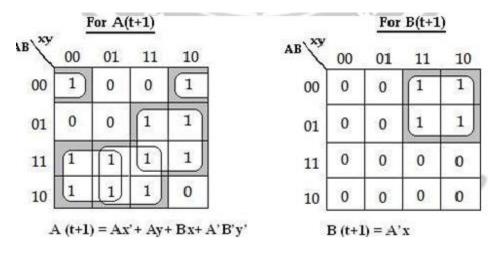

15.A sequential circuit has two flip flops A and B,two inputs x and y and one output z.the flip flop input equations and circuit output equations are:

JA=Bx+B'y' KA=B'xy'

J<sub>B</sub>=A'x

K<sub>B</sub>=A+xy'

Z=Ax'y'+Bx'y'

Draw the logic diagram and tabulate the state table.

State diagram:

# **STATE TABLE:**

| Pre | esent | Inp | out |                  | Flip-Flop        |                  |                  |        |        | Output |

|-----|-------|-----|-----|------------------|------------------|------------------|------------------|--------|--------|--------|

| st  | state |     |     | Inputs           |                  |                  |                  |        |        |        |

| Α   | В     | X   | у   | J <sub>A</sub> = | K <sub>A</sub> = | J <sub>B</sub> = | K <sub>B</sub> = | A(t+1) | B(t+1) | Z      |

|     |       |     |     | Bx+B'y'          | B'xy'            | A'x              | A+xy'            |        |        |        |

| 0   | 0     | 0   | 0   | 1                | 0                | 0                | 0                | 1      | 0      | 0      |

| 0   | 0     | 0   | 1   | 0                | 0                | 0                | 0                | 0      | 0      | 0      |

| 0   | 0     | 1   | 0   | 1                | 1                | 1                | 1                | 1      | 1      | 0      |

| 0   | 0     | 1   | 1   | 0                | 0                | 1                | 0                | 0      | 1      | 0      |

|     |       |     |     |                  |                  |                  |                  |        |        |        |

| i   | 1     | 1   | 1   | I                |                  | 1                |                  | I      |        |        |

| 0   | 1     | 0   | 0   | 0                | 0                | 0                | 0                | 0      | 0      | 1      |

| 0   | 1     | 0   | 1   | 0                | 0                | 0                | 0                | 0      | 0      | 0      |

| 0   | 1     | 1   | 0   | 1                | 0                | 1                | 1                | 1      | 1      | 0      |

| 0   | 1     | 1   | 1   | 1                | 0                | 1                | 0                | 1      | 1      | 0      |

| 1   | 0     | 0   | 0   | 1                | 0                | 0                | 1                | 1      | 0      | 1      |

| 1   | 0     | 0   | 1   | 0                | 0                | 0                | 1                | 1      | 0      | 0      |

| 1   | 0     | 1   | 0   | 1                | 1                | 0                | 1                | 0      | 0      | 0      |

| 1   | 0     | 1   | 1   | 0                | 0                | 0                | 1                | 1      | 0      | 0      |

| 1   | 1     | 0   | 0   | 0                | 0                | 0                | 1                | 1      | 0      | 1      |

| 1   | 1     | 0   | 1   | 0                | 0                | 0                | 1                | 1      | 0      | 0      |

| 1   | 1     | 1   | 0   | 1                | 0                | 0                | 1                | 1      | 0      | 0      |

| 1   | 1     | 1   | 1   | 1                | 0                | 0                | 1                | 1      | 0      | 0      |

|     |       |     |     |                  |                  |                  |                  |        |        |        |

|     |       |     |     |                  |                  |                  |                  |        |        |        |

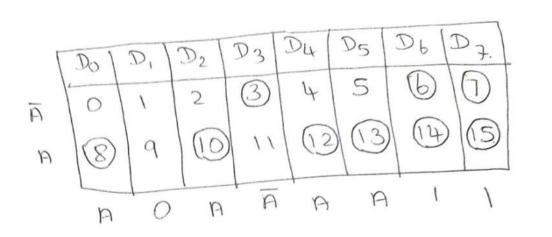

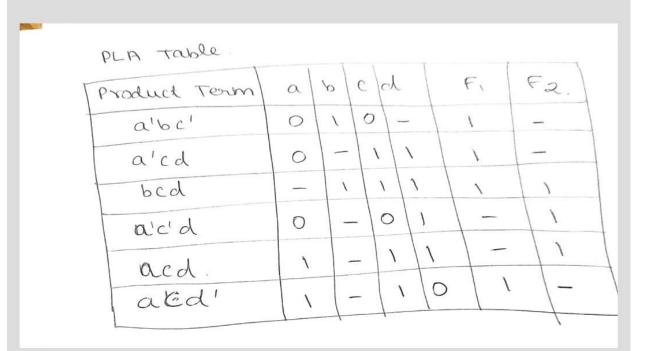

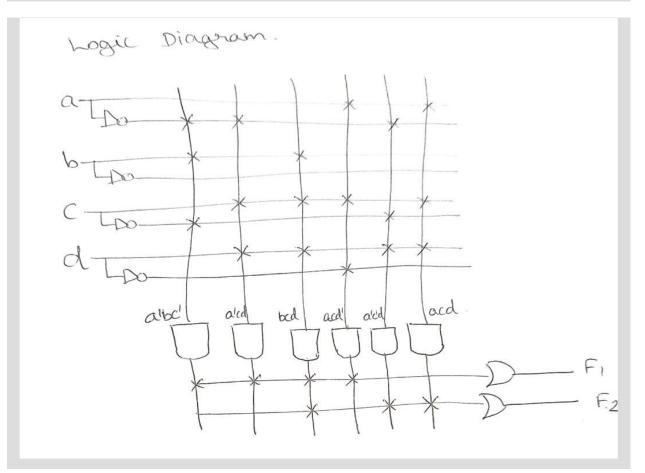

17.combinational logic is defined by the functions  $F=\pounds(3,4,5,7,10,14,15)$  AND  $\pounds(1,5,7,11,15)$ .IMPLEMENT the circuit using a programmable logic array with 4 inputs,6 product terms and 2 outputs.

8

Solution.  $F_1 = \sum (3, 4, 5, 7, 10, 14, 15)$  $F_2 = Em(1, 5, 7, 11, 15)$ K-map for Fi. ab/cd 01 11 10 00 1 01 1 ١ ITT 11 101 F, = a'bc' + a'cd + acd + bcd. K-may for F2: ab 00 01 11 10 00 01 1 11 IT 10 Fa= A'C'D + BCD + ACD.

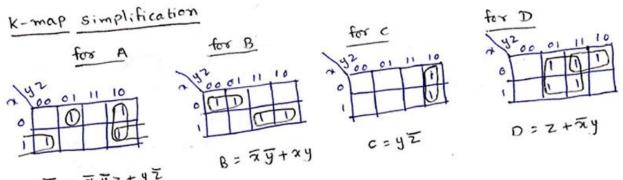

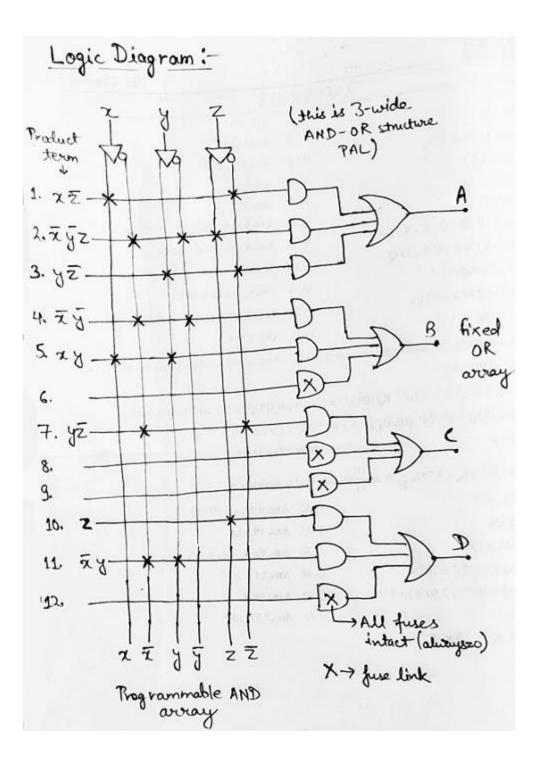

18. Tabulate the PAL programming table for the four Boolean functions listed below.

$A(x,y,z)=\pounds(1,2,4,6)$  $B(x,y,z)=\pounds(0,1,6,7)$

C(x,y,z)=£(2,6)

D(x,y,z) =£ (1,2,3,5,7).simplify using K-map.

A= x Z + x y Z+ y Z

| Program | Table   |

|---------|---------|

|         | Program |

|   | a la tomac    |   | AND imports |    |    | outputs     |

|---|---------------|---|-------------|----|----|-------------|

|   | Product terms |   | a           | Ч  | 2  |             |

|   | хī            |   | ١           | -  | 0  |             |

|   | ā ý z         | × | 0           | 0  | 1  | A=22+292+92 |

|   | 42            |   | -           | ١  | 0  |             |

| ł | व पु          |   | .0          | 0  | -  | B= スy+2y    |

|   | 29            |   | 1           | 1_ | 1  |             |

|   | 42            |   | 111         | 1  | 0  | C= 42       |

|   | Z             |   | -           | -  | 3  | D= Z+xy     |

|   | ay            |   | G           | 1  | 11 |             |

# **19.Interpret a Verilog HDL code to perform read and write operation of memory.**

# HDL Example 7.1

| <ul><li>// Read and write operations of memory</li><li>// Memory size is 64 words of four bits each.</li></ul> |                         |

|----------------------------------------------------------------------------------------------------------------|-------------------------|

| module memory (Enable, ReadWrite, Address                                                                      | , DataIn, DataOut);     |

| input Enable, ReadWrite;                                                                                       |                         |

| input [3: 0] Dataln;                                                                                           |                         |

| input [5: 0] Address;                                                                                          |                         |

| output [3: 0] DataOut;                                                                                         |                         |

| reg [3: 0] DataOut;                                                                                            |                         |

| reg [3: 0] Mem [0: 63];                                                                                        | // 64 x 4 memory        |

| always @ (Enable or ReadWrite)                                                                                 |                         |

| if (Enable)                                                                                                    |                         |

| if (ReadWrite) DataOut = Mem [Address];                                                                        | // Read                 |

| else Mem [Address] = Dataln;                                                                                   | // Write                |

| else DataOut = 4'bz;                                                                                           | // High impedance state |

| endmodule                                                                                                      | 5                       |

# OR

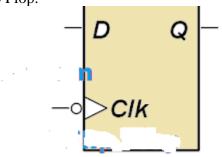

# 20.Design Verilog module for an edge triggered D Flip flop in the data flow model.

D Flip-Flop is a fundamental component in digital logic circuits. Verilog code for D Flip Flop is presented in this project. There are two types of D Flip-Flops being implemented which are Rising-Edge D Flip Flop and Falling-Edge D Flip Flop.

Rising-Edge D Flip-Flop

Falling-Edge D Flip-Flop

module RisingEdge\_DFlipFlop(D,clk,Q);

input D; // Data input

input clk; // clock input

output Q; // output Q

```

always @(posedge clk)

begin

Q <= D;

end

endmodule

```

```

module FallingEdge_DFlipFlop(D,clk,Q);

input D; // Data input

input clk; // clock input

output reg Q; // output Q

always @(negedge clk)

begin

Q <= D;

end

endmodule</pre>

```